VIA C7

C7-M 795 2.0 GHz | |

| General information | |

|---|---|

| Launched | May 2005 |

| Common manufacturer |

|

| Performance | |

| Max. CPU clock rate | 1.0 GHz to 2.0 GHz |

| FSB speeds | 400 MT/s to 800 MT/s |

| Cache | |

| L1 cache | 64 KiB instruction + 64 KiB data |

| L2 cache | 128 KiB 32-way exclusive |

| Architecture and classification | |

| Technology node | 90nm |

| Instruction set | x86-16, IA-32 |

| Extensions | |

| Physical specifications | |

| Cores |

|

| Sockets |

|

| Products, models, variants | |

| Core name |

|

| History | |

| Predecessor | VIA C3 |

| Successor | VIA Nano |

The VIA C7 is an x86 central processing unit designed by Centaur Technology and sold by VIA Technologies.

Product history

[edit]The C7 delivers a number of improvements to the older VIA C3 cores but is nearly identical to the latest VIA C3 Nehemiah core. The C7 was officially launched in May 2005, although according to market reports, full volume production was not in place at that date. In May 2006 Intel's cross-licensing agreement with VIA expired and was not renewed, which was the reason for the forced termination of C3 shipments on March 31, 2006, as VIA lost rights to the Socket 370.

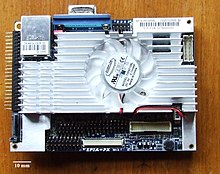

A 1 GHz C7 processor with 128kB of cache memory is used in VIA's own PX10000G motherboard which is based on the proprietary Pico-ITX form factor. The chip is cooled by a large heatsink that covers most of the board and a small 40mm fan.

In early April 2008 the schoolroom-use oriented, ultra-portable HP 2133 Mini-Note PC family debuted with an entirely VIA-based, 1.0, 1.2 and 1.6 GHz C7-M processor portfolio, where the lowest speed model is optimized for running an SSD-based 4GB Linux distribution with a sub $500 price tag, while the middle tier carries Windows XP and the top model comes with Windows Vista Business, factory default. HP chose the single-core VIA C7-M CPU in order to meet the already fixed $499 starting price, even though Intel's competing Atom processor line debuted on 2 April 2008.

The C7 is sold in five main versions:

- C7: for desktops / laptops (1.5-2.0 GHz) - FCPGA Pentium-M package, 400, 533, 800 MHz FSB

- C7-M: for mobiles / embedded (1.5-2.0 GHz) - NanoBGA2, 21mm × 21mm, 400, 800 MHz FSB

- C7-M Ultra Low Voltage: for mobiles / embedded (1.0-1.6 GHz) - NanoBGA2, 21mm × 21mm, 400, 800 MHz FSB

- C7-D: similar to original C7, but RoHS-compliant[1] and marketed as "carbon-free processor". Some variants do not support PowerSaver[citation needed]

- Eden: Some VIA Eden CPUs are based on a C7 core with low power consumption, package size, and clock rates as low as 400 MHz.

CPU cores

[edit]Esther

[edit]The Esther (C5J) is the next evolution step of the Nehemiah+ (C5P) core of the VIA C3 line-up.

New Features of this core include:

- Average power consumption of less than 1 watt.

- 2 GHz operation and a TDP of 20 watts.

- L2 cache increased from 64k to 128k, with associativity increased from 16-way set associative in C3 to 32-way set associative in C7.

- VIA has stated[2] the C7 bus is physically based upon the Pentium-M 479-pin packaging, but uses the proprietary VIA V4 bus for electrical signalling, instead of Intel’s AGTL+ Quad Pumped Bus, avoiding legal infringement.

- "Twin Turbo" technology, which consists of dual PLLs, one set at a high clock speed, and the other set at a lower speed. This allows the processor's clock frequency to be adjusted in a single processor cycle. Lower switching latency means that more aggressive regulation can be employed.

- Support for SSE2 and SSE3 extended instructions.

- NX bit in PAE mode that prevents buffer overflow software bugs from being exploitable by viruses or attackers.

- Hardware support for SHA-1 and SHA-256 hashing.

- Hardware based "Montgomery multiplier" supporting key sizes up to 32K for public-key cryptography.

Design choices

[edit]- C7 Esther as an evolutionary step after C3 Nehemiah, in which VIA / Centaur followed their traditional approach of balancing performance against a constrained transistor / power budget.

- The cornerstone of the C3 series chips' design philosophy has been that even a relatively simple in-order scalar core can offer reasonable performance against a complex superscalar out-of-order core if supported by an efficient "front-end", i.e. prefetch, cache and branch prediction mechanisms.

- In the case of C7, the design team have focused on further streamlining the (front-end) of the chip, i.e. cache size, associativity and throughput as well as the prefetch system.[3] At the same time no significant changes to the execution core (back-end) of the chip.

- The C7 successfully further closes the gap in performance with AMD / Intel chips, since clock speed is not thermally constrained.[citation needed]

See also

[edit]- List of VIA C7 microprocessors

- List of VIA Eden microprocessors

- List of VIA microprocessors

- Intel Atom

- Netbook

References

[edit]- ^ "FAQ on Green Computing & ROHS - VIA Technologies, Inc". VIA Connect. 2007-11-21. Archived from the original on 2007-11-21. Retrieved 2024-08-04.

- ^ Shilov, Anton. "VIA Denies Intel Pentium M Bus Licensing". X-bit labs. Archived from the original on 2007-05-13. Retrieved 2007-04-23.

- ^ "Detailed Platform Analysis in RightMark Memory Analyzer. Part 12: VIA C7/C7-M Processors". Pricenfees.com. Retrieved 2007-03-12.

Further reading

[edit]- Henry, G Glenn; Centaur Technology; Naivar, Gem (30 January 2006). "Random Stuff". How to make a highly secure x86 processor. UT-Austin Computer Architecture Seminar Series. University of Texas at Austin.

External links

[edit]- Smith, Van (2006-03-10). "An inside look at the VIA C7-M". VIA Arena. Archived from the original on 2014-02-21.

- Review of the EPIA EN15000 with VIA C7 Processor[usurped]

- VIA C7 Processor

- VIA C7-M Processor

- Detailed Platform Analysis in RightMark Memory Analyzer. Part 12: VIA C7/C7-M Processors, translated in English

- http://www.cpushack.com/VIA.html

- https://www.pricenfees.com/digit-life-archives/via-cyrix-iii-samuel-2-600-667-mhz

- https://web.archive.org/web/20060615180950/http://www.sandpile.org/impl/c5xl.htm