Bucks County, Pennsylvania

Bucks County | |

|---|---|

Bucks County Administration Building in Doylestown in 2010 | |

|

| |

Location within the U.S. state of Pennsylvania | |

Pennsylvania's location within the U.S. | |

| Coordinates: 40°20′N 75°07′W / 40.34°N 75.11°W | |

| Country | |

| State | |

| Founded | November 1682 |

| Named for | Buckinghamshire, England |

| Seat | Doylestown |

| Largest township | Bensalem |

| Area | |

• Total | 622 sq mi (1,610 km2) |

| • Land | 604 sq mi (1,560 km2) |

| • Water | 18 sq mi (50 km2) 2.8% |

| Population (2020) | |

• Total | 646,538 |

• Estimate (2023) | 645,984 |

| • Density | 1,070/sq mi (410/km2) |

| Time zone | UTC−5 (Eastern) |

| • Summer (DST) | UTC−4 (EDT) |

| Congressional district | 1st |

| Website | www |

| Designated | October 29, 1982[1] |

Bucks County is a county in the Commonwealth of Pennsylvania. As of the 2020 census, the population was 646,538,[2] making it the fourth-most populous county in Pennsylvania. Its county seat is Doylestown.[3] The county is named after the English county of Buckinghamshire. The county is part of the Southeast Pennsylvania region of the state.[a]

The county represents the northern boundary of the Philadelphia–Camden–Wilmington, PA–NJ–DE–MD metropolitan statistical area.

To its southwest, Bucks County borders Montgomery County and Philadelphia, the nation's sixth-largest city. To its east, the county borders the Delaware River and U.S. state of New Jersey. To its north, the county borders Lehigh and Northampton counties in the state's Lehigh Valley region. The county is approximately 30 miles (48 km) southeast of Allentown, the state's third-largest city, and 40 miles (64 km) north of Philadelphia, the state's largest city.

History

[edit]Founding

[edit]

Bucks County is one of the three original counties created by colonial proprietor William Penn in 1682. Penn named the county after Buckinghamshire, the county in which he lived in England; "Bucks." is the traditional abbreviation for the English county, which became the actual name of the Pennsylvania one. He built a country estate, Pennsbury Manor, in Falls Township in present-day Bucks County.

Some places in Bucks County were named after locations in Buckinghamshire, England, including Buckingham and Buckingham Township, named after the former county town of Buckinghamshire; Chalfont, named after Chalfont St Giles, the parish home of William Penn's first wife and the location of the Jordans Quaker Meeting House, where Penn is buried; Solebury, named after Soulbury, England; and Wycombe, named after the town of High Wycombe.

Bucks County was originally much larger than it is today. Northampton County was formed in 1752 from part of Bucks County, and Lehigh County was formed in 1812 from part of Northampton County.

American Revolutionary War

[edit]General George Washington and his troops camped in Bucks County as they prepared to cross the Delaware River to take Trenton, New Jersey, by surprise on the morning of December 26, 1776. Their successful attack on Britain's Hessian forces was a turning point in the American Revolutionary War. The town of Washington Crossing, Pennsylvania and Washington Crossing Historic Park were named to commemorate the event.

Geography

[edit]According to the U.S. Census Bureau, the county has a total area of 622 square miles (1,610 km2), of which 604 square miles (1,560 km2) is land and 18 square miles (47 km2) (2.8%) is water.[4]

The southern third of the county between Philadelphia and Trenton, New Jersey, often called Lower Bucks, resides in the Atlantic Coastal Plain; it is flat and near sea level, and is the county's most populated and industrialized area.

Bucks County shares a western border with Montgomery County, and also borders Philadelphia to the southwest, and Northampton and Lehigh Counties to the north. From north to south, it is linked to Warren, Hunterdon, Mercer and Burlington Counties in New Jersey by bridges.

Tohickon Creek and Neshaminy Creek are the largest tributaries of the Delaware in Bucks County. Tohickon Creek empties into the river at Point Pleasant and Neshaminy at Croydon (Bristol Township).

Adjacent counties

[edit]- Lehigh County (northwest)

- Northampton County (north)

- Warren County, New Jersey (northeast)

- Hunterdon County, New Jersey (northeast)

- Mercer County, New Jersey (east)

- Burlington County, New Jersey (southeast)

- Philadelphia County (south)

- Montgomery County (west)

Demographics

[edit]| Census | Pop. | Note | %± |

|---|---|---|---|

| 1790 | 25,216 | — | |

| 1800 | 27,496 | 9.0% | |

| 1810 | 32,371 | 17.7% | |

| 1820 | 37,842 | 16.9% | |

| 1830 | 45,745 | 20.9% | |

| 1840 | 48,107 | 5.2% | |

| 1850 | 56,091 | 16.6% | |

| 1860 | 63,578 | 13.3% | |

| 1870 | 64,336 | 1.2% | |

| 1880 | 68,656 | 6.7% | |

| 1890 | 70,615 | 2.9% | |

| 1900 | 71,190 | 0.8% | |

| 1910 | 76,530 | 7.5% | |

| 1920 | 82,476 | 7.8% | |

| 1930 | 96,727 | 17.3% | |

| 1940 | 107,715 | 11.4% | |

| 1950 | 144,620 | 34.3% | |

| 1960 | 308,567 | 113.4% | |

| 1970 | 410,056 | 32.9% | |

| 1980 | 479,211 | 16.9% | |

| 1990 | 541,174 | 12.9% | |

| 2000 | 597,635 | 10.4% | |

| 2010 | 625,249 | 4.6% | |

| 2020 | 646,538 | 3.4% | |

| U.S. Decennial Census[5] 1790-1960[6] 1900-1990[7] 1990-2000[8] 2010-2019[9] | |||

As of the 2010 census, there were 625,249 people. The population density was 1,034.7 people per square mile. The racial makeup of the county was 86.6% Non-Hispanic white, 3.9% Black or African American, 0.3% Native American, 4.1% Asian (2.1% Indian, 1.1% Chinese, 0.7% Korean, 0.5% Filipino, 0.3% Vietnamese, 0.1% Japanese, 0.4% other Asian) 0.1% Pacific Islander, 1.7% were of two or more races, and 1.5% were of other races. 4.4% of the population were Hispanic or Latino of any race.

As of the census[10] of 2000, there were 218,725 households, and 160,981 families residing in the county. There were 225,498 housing units at an average density of 371 per square mile (143/km2). 20.1% were of German, 19.1% Irish, 14.0% Italian, 7.5% English and 5.9% Polish ancestry.

There were 218,725 households, out of which 35.30% had children under the age of 18 living with them, 61.20% were married couples living together, 8.80% had a female householder with no husband present, and 26.40% were non-families. 21.50% of all households were made up of individuals, and 8.10% had someone living alone who was 65 years of age or older. The average household size was 2.69 and the average family size was 3.17.

In the county, the population was spread out, with 25.70% under the age of 18, 7.00% from 18 to 24, 30.70% from 25 to 44, 24.30% from 45 to 64, and 12.40% who were 65 years of age or older. The median age was 38 years. For every 100 females there were 96.30 males. For every 100 females age 18 and over, there were 93.40 males.

The median income for a household in the county was $59,727, and the median income for a family was $68,727. Males had a median income of $46,587 versus $31,984 for females. The per capita income for the county was $27,430. About 3.10% of families and 4.50% of the population were below the poverty line, including 4.80% of those under age 18 and 5.50% of those age 65 or over.

Population growth

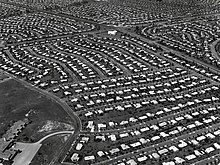

[edit]Growth began in the early 1950s, when William Levitt chose Bucks County for his second "Levittown". Levitt bought hundreds of acres of woodlands and farmland, and constructed 17,000 homes and dozens of schools, parks, libraries, and shopping centers. By the time the project was completed, the population of Levittown had swelled to nearly 74,000 residents. At the time, only whites could buy homes. This rule however, was soon overturned. Other planned developments included Croydon and Fairless Hills. This rapid sprawl continued until the mid-1960s.

In the 1970s, the county experienced a second growth spurt as developers expanded in previously underdeveloped townships, including Middletown, Lower Makefield, Northampton, and Newtown townships. Tract housing, office complexes, shopping centers, and sprawling parking lots continued to move more and more towards Upper Bucks, swallowing horse farms, sprawling forests, and wetlands. Oxford Valley Mall was constructed in Middletown, and became a retail nucleus in the county.

In the late 20th century, growth somewhat stabilized as development was completed in the county's historically underdeveloped areas, leaving little new area to be further developed.

Bucks County areas along the Delaware River have surpluses of abandoned industry, so many municipalities have granted building rights to luxury housing developers. As the regions that began the suburban boom in Bucks County, such as Levittown, have aged, commercial strips and other neglected structures have been torn down and replaced with new shopping plazas and commercial chains. With rising property values, areas with older construction are undergoing a renaissance, and Central and Upper Bucks have continued to experience rapid growth, with many municipalities doubling their populations since the late 20th century.

As of 2013, the population of Bucks County was 626,976, making it the fourth-most populous county in the state behind Philadelphia, Allegheny, and Montgomery counties.[9]

2020 census

[edit]| Race | Num. | Perc. |

|---|---|---|

| White (NH) | 521,575 | 80.67% |

| Black or African American (NH) | 25,277 | 4% |

| Native American (NH) | 531 | 0.08% |

| Asian (NH) | 35,053 | 5.42% |

| Pacific Islander (NH) | 143 | 0.02% |

| Other/Mixed (NH) | 24,189 | 3.74% |

| Hispanic or Latino | 39,770 | 6.15% |

Economy

[edit]

The boroughs of Bristol and Morrisville were prominent industrial centers along the Northeast Corridor during World War II. Suburban development accelerated in Lower Bucks in the 1950s with the opening of Levittown, Pennsylvania, the second such "Levittown" designed by William Levitt.

Among Bucks' largest employers in the twentieth century were U.S. Steel in Falls Township, and the Vulcanized Rubber & Plastics and Robertson Tile companies in Morrisville. Rohm and Haas continues to operate several chemical plants around Bristol. Waste Management operates a landfill in Tullytown that is the largest receptacle of out-of-state waste in the USA (receiving much of New York City's waste following the closure of Fresh Kills landfill in Staten Island, NY 40 miles (64 km) away).[citation needed]

Bucks is also experiencing rapid growth in biotechnology, along with neighboring Montgomery County. The Greater Philadelphia area consistently ranks in the top 10 geographic clusters for biotechnology and biopharma.[12] It is projected by 2020 that one out of four people in Bucks County will work in biotechnology.

Notable businesses

[edit]- 21st Century Media

- Burpee Seeds and Plants

- Byers' Choice Ltd.

- Carson Helicopters

- Charming Shoppes

- eGames, Inc.

- EPAM Systems

- GE Betz

- Keystone Aircraft

- V. La Rosa and Sons Macaroni Company

- Lehigh Defense

- McCaffrey's Food Markets

- Moon Nurseries

- New Hope and Ivyland Railroad

- Questar Corporation

- Rita's Italian Ice

- Simpay

- West Coast Video

- Windowizards

Tourism

[edit]

Another important asset of the county is tourism. The county's northern regions, colloquially referred to as Upper Bucks, are known for their natural scenery, farmland, colonial history, and proximity to major urban areas, including Philadelphia, New York City, Allentown, Reading, and Atlantic City, each of which is within a two-hour driving radius.

Bucks County is home to twelve covered bridges. Ten are still open to vehicular traffic; two others, located in parks, are open only to non-vehicular traffic. All Bucks County bridges use the Town truss design. Schofield Ford Bridge, in Tyler State Park, was reconstructed in 1997 from the ground up after arsonists destroyed the original in 1991.[13]

Popular attractions in Bucks County include the shops and studios of New Hope, Peddler's Village (in Lahaska), Washington Crossing Historic Park, New Hope Railroad, Bucks County River Country and Bucks County Playhouse Theater (in New Hope). Rice's Market near Lahaska is a popular destination on Tuesday mornings. Quakertown Farmer's Market (locally called "Q-Mart") is a popular shopping destination on weekends. The county seat of Doylestown has the trifecta of concrete structures built by Henry Chapman Mercer, including the Moravian Pottery and Tile Works, the Mercer Museum and Fonthill, Mercer's personal home.

Southern Bucks, colloquially referred to as Lower Bucks, is home to two important shopping malls, Neshaminy Mall, Oxford Valley Mall, and Sesame Place, a family theme park based on the Sesame Street television series. Also within Lower Bucks County is Parx Casino and Racing in Bensalem, a casino and thoroughbred horse racing track. The casino was built on the grounds of what was originally Philadelphia Park Racetrack. The complex includes the thoroughbred horse racing track, expansive casino, a dance club, numerous dining options, and the Xcite Center.

Education

[edit]Colleges and universities

[edit]Public school districts

[edit]

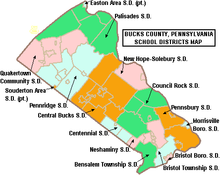

K-12 school districts include:[14]

- Bensalem Township School District

- Bristol Borough School District

- Bristol Township School District

- Centennial School District

- Central Bucks School District

- Council Rock School District

- Morrisville Borough School District

- Neshaminy School District

- New Hope-Solebury School District

- North Penn School District (also in Montgomery County)

- Palisades School District

- Pennridge School District

- Pennsbury School District

- Quakertown Community School District

- Souderton Area School District (also in Montgomery County)

The Bucks County public schools listed above are served by a regional educational service agency called the Bucks County Intermediate Unit #22 located in the county seat of Doylestown.

Public charter schools

[edit]- Bucks County Montessori Charter School

- Center Student Learning Charter School

- School Lane Charter School

Private schools

[edit]- 27 Catholic grade schools under jurisdiction of the Archdiocese of Philadelphia

- Abrams Hebrew Academy (K–8)

- Archbishop Wood Catholic High School

- Calvary Christian School

- Conwell-Egan Catholic High School

- George School

- Holy Family Regional Catholic School

- Holy Ghost Preparatory School (9–12 for boys)

- Newtown Friends School (PreK-8)

- Plumstead Christian School

- Quakertown Christian School

- Solebury School

- St. Katherine Drexel

- St. Michael the Archangel

- The Pen Ryn School

- Trevose Day School

- United Friends School Quakertown[15]

- Villa Joseph Marie High School (9–12 for girls)

Community, junior, and technical colleges

[edit]Libraries

[edit]The Bucks County Library System was founded in 1956 by a resolution of the Bucks County Commissioners.[16]

The Bucks County Library System is made up of 7 branch libraries in the following townships:

- Bensalem

- Doylestown

- Langhorne

- Levittown

- Perkasie

- Quakerstown

- Yardley-Makefield

Arts and culture

[edit]Fine and performing arts

[edit]Many artists and writers based in New York City have called Bucks County home, settling mainly in the small stretch between Doylestown and New Hope and along the Delaware River. Notable residents have included Margaret Mead, Pearl S. Buck, Oscar Hammerstein II, Stephen Sondheim, Charlie Parker, Moss Hart, George S. Kaufman, James Michener, Dorothy Parker, S. J. Perelman, Stan and Jan Berenstain, Daniel Garber, Alfred Bester, Annie Haslam, and Jean Toomer. Bucks County has been the home of writer/musician James McBride, writer Eric Knight, Academy Award-winning film composer Joe Renzetti, musician Gene Ween of Ween, painter Christopher Wajda, photographer Michael Barone, and furniture designer George Nakashima. James Gould Cozzens lived in Lambertville, New Jersey, just across the river from Bucks County, and used Doylestown as the model for the setting of two novels; he is considered a Bucks County artist. Allen Saalburg relocated to Bucks County in 1947, and named his press after the canal.[17]

The county boasts many local theater companies, including the long-established and recently reopened Bucks County Playhouse in New Hope, Town and Country Players in Buckingham, ActorsNET in Morrisville, and the Bristol Riverside Theatre, a professional Equity theater in Bristol. The Bucks County Symphony, founded in 1953, performs in Doylestown throughout the year and the Bucks County Gilbert & Sullivan Society, founded in 2009, performs a Gilbert & Sullivan operetta with full orchestra each June.

The Wild River Review, an online magazine that publishes in-depth reporting, works of literature, art, visual art, reviews, interviews, and columns by and about contemporary artists, photographers, and writers, is based out of Doylestown.

Literature

[edit]The partially autobiographical novel The Fires of Spring by James Michener takes place in and around Doylestown.

Popular culture

[edit]Alecia Moore, more commonly known as Pink, was born in Doylestown, as was motion picture writer and director Stefan Avalos. Three American Idol contestants live in Bucks County: Justin Guarini, who was born in Atlanta, but moved to Bucks County; Jordan White, who was born in Cranford, New Jersey and moved to Bucks County; and Anthony Fedorov, who was born in Ukraine and was from Trevose, in Lower Southampton Township. Singer/actress Irene Molloy and classical tenor David Gordon were born in Doylestown. Musician Asher Roth was born in Morrisville. The Tony Award-winning Broadway play Vanya and Sonia and Masha and Spike is set in the county. The main members of the rock band Ween are from New Hope.[18] Pop star Sabrina Carpenter was born in Quakertown, and grew up in nearby Montgomery County.

Film

[edit]- The 2019 film Colewell, starring Karen Allen, dedicated to Marguerite Addis a lifelong resident of Bucks County.

- The 2012 film Safe, starring Jason Statham, was filmed at the Parx Casino and Racing in Bensalem Township.[19]

- The 2012 film The Discoverers[20] was filmed in a variety of locations in Bucks County, including Croydon, Bristol, Newtown, New Hope, and Tyler State Park.[20][21]

- The 2010 NBC pilot episode for Outlaw was filmed in the Andalusia section of Bensalem Township.[22][23]

- Bucks County is mentioned multiple times on the 2010 Freeform TV series Pretty Little Liars.

- The 2009 film Law Abiding Citizen, starring Gerard Butler and Jamie Foxx, was filmed partially in New Hope.[24]

- The county fair scene in the 2006 film Charlotte's Web was filmed at the Southampton Days Fair in Southampton.

- M. Night Shyamalan's 2002 film Signs, starring Mel Gibson, was filmed and takes place in Bucks County. The town scenes were filmed on State Street in Newtown Borough, and the drugstore scene was filmed at Burns' Pharmacy on Pennsylvania Avenue in Morrisville. The house was built on farmland privately owned and leased to Delaware Valley College in Doylestown Township. A stage set for some interior shots was created in a warehouse on State Road in Bensalem Township. Shyamalan's film Lady in the Water was shot across the street from the Bloomsdale section of Bristol Township. In addition, Shyamalan's 2008 film, The Happening, was filmed in Upper Bucks County, including Plumsteadville.[25][26]

- Central Bucks High School West football team was followed during the 1999 season for the documentary The Last Game.[27]

- With the exception of the footage filmed in the New Jersey Pine Barrens, all of the 1998 film The Last Broadcast was shot in Bucks County.

- A short scene from Stephen King's The Stand, published in 1978, is based in Pipersville.

- The producer Fred Bauer, the director Steve Rash and composer Joseph Renzetti of The Buddy Holly Story, released in 1978, all live in Bucks County, where the film was conceived, and written by Bob Gittler.

- One of Steven Spielberg's earliest films, Something Evil, released in 1972, is set in Bucks County.

- The 1942 film George Washington Slept Here was set chiefly in Bucks County, although most of the filming took place in the studio.

Media

[edit]Local print publications include Bucks County Courier Times, The Intelligencer, The Advance of Bucks County, Bucks County Herald, Bucks County Town and Country Living, Radius Magazine, Yardley Voice, Morrisville Times, Newtown Gazette, Northampton Herald, Langhorne Ledger, Lower Southampton Spirit, New Hope News, Doylestown Observer, Warwick Journal, Fairless Focus. Online news publications are Levittown Now, Bucks County Beacon, NewtownPANow, Bucks Happening, New Hope Free Press. WBCB is a local radio news station.

Sports

[edit]Rugby league

[edit]The Bucks County Sharks rugby league team played in the AMNRL from 1997 to 2010 season.[28] They returned to play in the AMNRL in 2011, until the league's fold in 2014, when they subsequently joined the USARL.[29]

Little League

[edit]The county has a considerable history of producing Little League baseball contenders. Since its inception in 1947, four of the seven Pennsylvania teams to compete in the Little League World Series in Williamsport, Pennsylvania have come from Bucks County: Morrisville (1955), Levittown American (1960 and 1961), and Council Rock-Newtown (2005). Two of these squads, Morrisville and Levittown (1960), went on to win the World Series title. In 2007, Council Rock Northampton won the PA State championship, and lost in the finals of regionals.

PIAA

[edit]The county is a part of PIAA's District I, and has seen many schools capture multiple state titles.

American Legion baseball

[edit]In 1996, Yardley Western Post 317 won the American Legion National Championship.

Bristol Legion Post 382 recently won the 2011 American Legion State Championship.

Horse racing

[edit]- Parx Casino and Racing, formerly Philadelphia Park Racetrack and Keystone Racetrack, was the former home of Triple Crown contender Smarty Jones, is in Bensalem.

Parks and recreation

[edit]Pennsylvania state parks

[edit]

There are six Commonwealth-owned parks in Bucks County:

- Five are owned and operated by the Pennsylvania Bureau of State Parks, part of the Pennsylvania Department of Conservation and Natural Resources (DCNR).

- Bucks County Parks and Recreation operates an 18-bed youth hostel in the Nockamixon State Park Weisel estate. The hostel is part of Hostelling International USA.[30]

- Washington Crossing Historic Park, a 500 acres (200 ha) site operated by the Pennsylvania Historical and Museum Commission, is part of Washington's Crossing, a U.S. National Historic Landmark area. The park is headquartered in the village of Washington Crossing located in Upper Makefield Township. It marks the location of George Washington's crossing of the Delaware River during the American Revolutionary War.

County parks

[edit]

- Bucks County Horse Park[31]

- Core Creek Park

- Dark Hollow Park[32]

- Lake Towhee Park

- Peace Valley Park

- Playwicki Park

- Ringing Rocks Park

- Silver Lake Park

- Tinicum Park

- Tohickon Valley Park

Historic properties

[edit]

- Moravian Pottery and Tile Works

- Stover-Myers Mill and Erwin Stover House

- Moland House an old stone farmhouse built around 1750 located in Warwick Township, served as the headquarters for General George Washington during the American Revolutionary War from August 10, 1777, until August 23, 1777.

- Summerseat, also known as the George Clymer House and Thomas Barclay House, is a historic house museum in Morrisville, built about 1765. It is the only house known to have been owned by two signers of the Declaration of Independence, George Clymer and Robert Morris, and as a headquarters of General George Washington from December 8 to 14, 1776, prior to Washington's attack in the Battle of Trenton.

- Pennsbury Manor house and grounds, the home of William Penn, founder and first Governor of Pennsylvania, administered by the Pennsylvania Historical and Museum Commission in association with the Pennsbury Society and are open to the public.[33]

County recreation sites

[edit]- Frosty Hollow Tennis Center

- Core Creek Tennis Center

- Oxford Valley Golf Course

- Oxford Valley Pool

- Tohickon Valley Pool

- Weisel Hostel

- Peace Valley Boat Rental

- Core Creek Boat Rental

County nature centers

[edit]- Bucks County Audubon Society's Honey Hollow Environmental Education Center

- Churchville Nature Center]

- Clark Nature Center

- Peace Valley Nature Center

- Silver Lake Nature Center

Transportation

[edit]Airports

[edit]Air transportation facilities available in or close to Bucks County include:

- Doylestown Airport

- Pennridge Airport

- Philadelphia International Airport[34]

- Quakertown Airport

- Sterling Aviation Heliport in Croydon next to Neshaminy State Park

- Van Sant Airport and Park

- Trenton-Mercer Airport

Public transportation

[edit]- Amtrak's Northeast Corridor line, which runs in southern Bucks County. Its Keystone Service trains run daily, stopping at the Cornwells Heights station in Bensalem Township

- Bucks County Transport, a paratransit and ridesharing service

- Doylestown Dart provides public transportation around the Doylestown area

- SEPTA

- City Division and Suburban Division bus routes across southeastern Bucks County

- Regional Rail's Lansdale/Doylestown, Trenton, Warminster and West Trenton lines

- TMA Bucks's Rushbus, which runs in parts of southern and central Bucks County

Major roads and highways

[edit]

Politics and government

[edit]| Year | Republican | Democratic | Third party(ies) | |||

|---|---|---|---|---|---|---|

| No. | % | No. | % | No. | % | |

| 2024 | 198,722 | 49.39% | 198,431 | 49.32% | 5,196 | 1.29% |

| 2020 | 187,367 | 47.16% | 204,712 | 51.53% | 5,212 | 1.31% |

| 2016 | 164,361 | 47.64% | 167,060 | 48.42% | 13,621 | 3.95% |

| 2012 | 156,579 | 48.74% | 160,521 | 49.97% | 4,166 | 1.30% |

| 2008 | 150,248 | 45.08% | 179,031 | 53.71% | 4,045 | 1.21% |

| 2004 | 154,469 | 48.30% | 163,438 | 51.10% | 1,909 | 0.60% |

| 2000 | 121,927 | 46.29% | 132,914 | 50.46% | 8,581 | 3.26% |

| 1996 | 94,899 | 41.74% | 103,313 | 45.44% | 29,151 | 12.82% |

| 1992 | 94,584 | 38.06% | 97,902 | 39.40% | 56,021 | 22.54% |

| 1988 | 127,563 | 59.99% | 82,472 | 38.78% | 2,605 | 1.23% |

| 1984 | 130,119 | 63.25% | 74,568 | 36.25% | 1,032 | 0.50% |

| 1980 | 100,536 | 55.49% | 59,120 | 32.63% | 21,508 | 11.87% |

| 1976 | 85,628 | 50.69% | 79,838 | 47.26% | 3,457 | 2.05% |

| 1972 | 99,684 | 62.28% | 56,784 | 35.48% | 3,591 | 2.24% |

| 1968 | 69,646 | 48.63% | 57,634 | 40.24% | 15,931 | 11.12% |

| 1964 | 50,243 | 38.89% | 78,287 | 60.60% | 646 | 0.50% |

| 1960 | 67,501 | 53.95% | 57,177 | 45.70% | 438 | 0.35% |

| 1956 | 59,862 | 60.72% | 38,541 | 39.09% | 180 | 0.18% |

| 1952 | 40,753 | 62.38% | 24,301 | 37.20% | 275 | 0.42% |

| 1948 | 29,411 | 62.46% | 16,655 | 35.37% | 1,018 | 2.16% |

| 1944 | 25,634 | 58.62% | 17,823 | 40.76% | 270 | 0.62% |

| 1940 | 25,169 | 54.73% | 20,586 | 44.77% | 229 | 0.50% |

| 1936 | 23,860 | 48.80% | 24,159 | 49.41% | 876 | 1.79% |

| 1932 | 22,331 | 59.07% | 14,135 | 37.39% | 1,341 | 3.55% |

| 1928 | 28,421 | 76.47% | 8,446 | 22.72% | 301 | 0.81% |

| 1924 | 17,460 | 66.88% | 6,582 | 25.21% | 2,066 | 7.91% |

| 1920 | 14,130 | 65.17% | 6,867 | 31.67% | 684 | 3.15% |

| 1916 | 9,269 | 53.97% | 7,491 | 43.62% | 414 | 2.41% |

| 1912 | 5,452 | 32.00% | 6,773 | 39.75% | 4,812 | 28.24% |

| 1908 | 9,409 | 55.33% | 7,233 | 42.54% | 362 | 2.13% |

| 1904 | 9,572 | 57.73% | 6,719 | 40.52% | 290 | 1.75% |

| 1900 | 9,263 | 55.13% | 7,287 | 43.37% | 253 | 1.51% |

| 1896 | 9,798 | 57.61% | 6,685 | 39.31% | 524 | 3.08% |

| 1892 | 8,230 | 48.72% | 8,390 | 49.67% | 272 | 1.61% |

| 1888 | 8,584 | 49.11% | 8,642 | 49.44% | 253 | 1.45% |

| 1884 | 8,191 | 48.47% | 8,604 | 50.92% | 103 | 0.61% |

| 1880 | 8,385 | 49.19% | 8,627 | 50.61% | 35 | 0.21% |

Like most of the Philadelphia suburbs, Bucks County was once a stronghold for the Republican Party. However, in recent years it has become more of a swing county, like Pennsylvania at large.

In presidential elections, Bucks County has been swept up in the overall Democratic trend that has swept the Philadelphia area, although the trend in Bucks has been less pronounced than in Delaware and Montgomery counties. It went Democratic in every presidential election from 1992 to 2020, though by a margin of less than 5% in each except for 2008, with three of those eight elections decided by less than 2% (1992, 2012, and 2016). In 2024, Donald Trump flipped the county with a victory margin of 0.07% or 291 votes. Prior to this Republicans won the county all but thrice between 1896 and 1988 (except in 1912, 1936, and 1964). Unlike most other suburban Philadelphia counties, Bucks County consistently voted Democratic during the Civil War era, only voting Republican twice between 1856 and 1892, in 1860 and 1872.

The executive government is run by a three-seat board of commissioners, one member of which serves as chairperson. Commissioners are elected through at-large voting and serve four-year terms. In cases of vacancy, a panel of county judges appoints members to fill seats. The current commissioners are Diane M. Ellis-Marseglia (D) (chairwoman), Robert "Bob" J. Harvie Jr. (D) (Vice-chairman), and Gene DiGirolamo (R). The current terms expire in January 2028.[36] In 2012, four county employees were sentenced for compensating public employees for political work on behalf of Republican candidates.[37]

Bucks County is represented in U.S. Congress by Pennsylvania's 1st congressional district, (map) formerly numbered as the 8th District. The district is represented by Brian Fitzpatrick (R), making this district one of 18 nationwide to be held by a Republican and won by Joe Biden in 2020.

In the 2016 elections, Democrats Hillary Clinton (President), Josh Shapiro (Attorney General), and Joe Torsella (State Treasurer) won Bucks County while Republicans Pat Toomey (U.S. Senate), Brian Fitzpatrick (U.S. Representative), and John Brown (Auditor General) won Bucks County in their respective races.[38]

The 2024 elections were mired in controversy in Bucks County, culminating in widespread condemnation of Bucks County Commissioner Diane Ellis-Marseglia (D), who was filmed on video stating that the "rule of law doesn't matter anymore in this country" in the context of a decision made by the county's Board of Elections to violate the PA State Supreme Court's ruling regarding which provisional ballots can and cannot be counted. [39]

Voter registration

[edit]Chart of Voter Registration

As of July 22, 2024, there are 478,085 registered voters in Bucks County.[40]

- Republican: 198,045 (41.42%)

- Democratic: 197,781 (41.37%)

- Independent: 61,061 (12.77%)

- Third Party: 21,198 (4.43%)

County commissioners

[edit]- Diane M. Ellis-Marseglia, chair, Democratic

- Robert "Bob" J. Harvie Jr., Vice Chair, Democratic

- Gene DiGirolamo, Republican

County row officers

[edit]| Office[41] | Official | Party | Term ends |

|---|---|---|---|

| Clerk of Courts | Eileen Hartnett Albillar | Democratic | 2027 |

| Controller | Pamela A. Van Blunk | Republican | 2025 |

| Coroner | Patti Campi | Democratic | 2027 |

| Treasurer | Kris Ballerini | Democratic | 2027 |

| District Attorney | Jennifer Schorn | Republican | 2025 |

| Prothonotary | Coleen Christian | Republican | 2025 |

| Recorder of Deeds | Daniel "Dan" McPhillips | Republican | 2025 |

| Register of Wills | Linda Bobrin | Democratic | 2027 |

| Sheriff | Frederick "Fred" A. Harran | Republican | 2025 |

Law enforcement

[edit]The current Bucks County Sheriff is Frederick "Fred" A. Harran.[42] Three members of the Sheriff's Office have died in the line of duty. One was shot and two others died in traffic accidents. The first, Sheriff Abram Kulp was murdered in February 1927.[43]

State senate

[edit]| District | Senator | Party |

|---|---|---|

| 6 | Frank Farry | Republican |

| 10 | Steve Santarsiero | Democratic |

| 16 | Jarrett Coleman | Republican |

State House of Representatives

[edit]United States House of Representatives

[edit]| District | Representative | Party |

|---|---|---|

| 1 | Brian Fitzpatrick | Republican |

United States Senate

[edit]| Senator | Party |

|---|---|

| Bob Casey | Democratic |

| John Fetterman | Democratic |

Communities

[edit]

Under Pennsylvania law, there are four types of incorporated municipalities: cities, boroughs, townships, and, in at most two cases, towns. The most populous borough in the county is Morrisville with 10,023 as of the 2000 census. The following boroughs and townships are located in Bucks County:

Boroughs

[edit]Townships

[edit]- Bedminster

- Bensalem

- Bridgeton

- Bristol

- Buckingham

- Doylestown

- Durham

- East Rockhill

- Falls

- Haycock

- Hilltown

- Lower Makefield

- Lower Southampton

- Middletown

- Milford

- New Britain

- Newtown

- Nockamixon

- Northampton

- Plumstead

- Richland

- Solebury

- Springfield

- Tinicum

- Upper Makefield

- Upper Southampton

- Warminster

- Warrington

- Warwick

- West Rockhill

- Wrightstown

Census-designated places

[edit]Census-designated places are geographical areas designated by the U.S. Census Bureau for the purposes of compiling demographic data. They are not actual jurisdictions under Pennsylvania law. Other unincorporated communities, such as villages, may be listed here as well.

Unincorporated communities

[edit]- Almont

- Andalusia

- Applebachsville

- Aquetong

- Argus

- Bedminster

- Blooming Glen

- Brick Tavern

- Bryn Gweled

- Buckingham

- Bucksville

- California

- Carversville

- Center Bridge

- Danboro

- Dolington

- Durham

- Elephant

- Erwinna

- Eureka

- Fallsington

- Ferndale

- Finland

- Forest Grove

- Fountainville

- Furlong

- Gallows Hill

- Gardenville

- Geryville‡

- Hagersville

- Harriman

- Harrow

- Hartsville

- Highton

- Hillside Village

- Hilltop

- Hilltown

- Hinkletown

- Holicong

- Holland

- Hood

- Jamison

- Johnsville

- Kintnersville

- Kulps Corner

- Lahaska

- Line Lexington‡

- Lodi

- Loux Corner (Hilltown)

- Lumberville

- Maple Beach

- Mechanicsville

- Mount Pleasant

- Neshaminy Falls

- Newville

- Oakford

- Ottsville

- Oxford Valley

- Paletown

- Passer

- Penns Park

- Pineville

- Pipersville

- Pleasant Valley

- Point Pleasant

- Revere

- Rushland

- Shelly

- Solebury

- Southampton

- Springtown

- Strawntown

- Uhlerstown

- Unionville‡

- Upper Black Eddy

- Washington Crossing

- White Horse

- Wrightstown

- Wycombe

- Zionhill

‡This populated place also has portions in an adjacent county or counties

Historic communities

[edit]- Tohickon, located under modern Lake Nockamixon

Police agencies and services

[edit]Population ranking

[edit]The population ranking of the following table is based on the 2010 census of Bucks County.[44]

† county seat

| Rank | City/Town/etc. | Municipal type | Population (2010 Census) |

|---|---|---|---|

| 1 | Bensalem | Township | 60,427 |

| 2 | Levittown | CDP | 52,983 |

| 3 | Croydon | CDP | 9,950 |

| 4 | Bristol | Borough | 9,726 |

| 5 | Quakertown | Borough | 8,979 |

| 6 | Morrisville | Borough | 8,728 |

| 7 | Perkasie | Borough | 8,511 |

| 8 | Fairless Hills | CDP | 8,466 |

| 9 | † Doylestown | Borough | 8,380 |

| 10 | Richboro | CDP | 6,563 |

| 11 | Telford (lies partially in Montgomery County) | Borough | 4,872 |

| 12 | Sellersville | Borough | 4,249 |

| 13 | Churchville | CDP | 4,128 |

| 14 | Warminster Heights | CDP | 4,124 |

| 15 | Chalfont | Borough | 4,009 |

| 16 | Village Shires | CDP | 3,949 |

| 17 | Woodbourne | CDP | 3,851 |

| 18 | Brittany Farms-The Highlands | CDP | 3,695 |

| 19 | Newtown Grant | CDP | 3,620 |

| 20 | Trevose | CDP | 3,550 |

| 21 | New Britain | Borough | 3,152 |

| 22 | Feasterville | CDP | 3,074 |

| 23 | Plumsteadville | CDP | 2,637 |

| 24 | New Hope | Borough | 2,528 |

| 25 | Yardley | Borough | 2,434 |

| 26 | Woodside | CDP | 2,425 |

| 27 | Penndel | Borough | 2,328 |

| 28 | Newtown | Borough | 2,248 |

| 29 | Dublin | Borough | 2,158 |

| 30 | Eddington | CDP | 1,906 |

| 31 | Tullytown | Borough | 1,872 |

| 32 | Spinnerstown | CDP | 1,826 |

| 33 | Langhorne | Borough | 1,622 |

| 34 | Langhorne Manor | Borough | 1,442 |

| 35 | Cornwells Heights | CDP | 1,391 |

| 36 | Richlandtown | Borough | 1,327 |

| 37 | Ivyland | Borough | 1,041 |

| 38 | Hulmeville | Borough | 1,003 |

| 39 | Trumbauersville | Borough | 974 |

| 40 | Milford Square | CDP | 897 |

| 41 | Silverdale | Borough | 871 |

| 42 | Riegelsville | Borough | 868 |

Climate

[edit]Piedmont Region

[edit]According to the Trewartha climate classification system, the Piedmont (United States) section of Bucks County, which is located roughly northwest of U.S. Route 1, has a Temperate Continental Climate with hot and slightly humid summers, cold winters and year-around precipitation (Dcao). Dcao climates are characterized by at least one month having an average mean temperature ≤ 32.0 °F (0 °C), four to seven months with an average mean temperature ≥ 50.0 °F (10 °C), at least one month with an average mean temperature ≥ 72.0 °F (22 °C) and no significant precipitation difference between seasons. According to the Köppen climate classification system, the climate is a hot-summer, wet all year, humid continental climate (Dfa). During the summer months in the Piedmont, episodes of extreme heat and humidity can occur with heat index values > 102 °F (39 °C). The average wettest month is July which corresponds with the annual peak in thunderstorm activity.

During the winter months, episodes of extreme cold and wind can occur with wind chill values < −16 °F (−27 °C). The plant hardiness zone at Haycock Mountain, elevation 968 ft (295 m), is 6b with an average annual extreme minimum air temperature of −4.6 °F (−20 °C).[45] The average seasonal (Nov-Apr) snowfall total is between 26 and 36 inches (66 and 91 centimetres) depending on elevation and distance from the Atlantic Ocean. The average snowiest month is February which correlates with the annual peak in nor'easter activity. Some areas of the Piedmont farther south and along the river below New Hope are in hardiness zone 7a, as is the Atlantic Coastal Plain region of Bucks.

| Climate data for Haycock Twp. Elevation: 735 ft (224 m). 1981-2010 Averages (1981-2018 Records) | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Month | Jan | Feb | Mar | Apr | May | Jun | Jul | Aug | Sep | Oct | Nov | Dec | Year |

| Record high °F (°C) | 69.9 (21.1) |

77.8 (25.4) |

86.8 (30.4) |

93.1 (33.9) |

93.9 (34.4) |

94.5 (34.7) |

101.4 (38.6) |

98.6 (37.0) |

96.3 (35.7) |

88.9 (31.6) |

79.6 (26.4) |

73.7 (23.2) |

101.4 (38.6) |

| Mean daily maximum °F (°C) | 37.3 (2.9) |

41.1 (5.1) |

49.1 (9.5) |

61.3 (16.3) |

71.0 (21.7) |

79.2 (26.2) |

83.5 (28.6) |

81.9 (27.7) |

75.2 (24.0) |

64.1 (17.8) |

53.4 (11.9) |

41.7 (5.4) |

61.7 (16.5) |

| Daily mean °F (°C) | 28.4 (−2.0) |

31.4 (−0.3) |

38.7 (3.7) |

49.9 (9.9) |

59.7 (15.4) |

68.4 (20.2) |

72.8 (22.7) |

71.4 (21.9) |

64.3 (17.9) |

53.3 (11.8) |

43.7 (6.5) |

33.2 (0.7) |

51.4 (10.8) |

| Mean daily minimum °F (°C) | 19.5 (−6.9) |

21.7 (−5.7) |

28.4 (−2.0) |

38.4 (3.6) |

48.3 (9.1) |

57.7 (14.3) |

62.1 (16.7) |

60.9 (16.1) |

53.4 (11.9) |

42.5 (5.8) |

34.0 (1.1) |

24.7 (−4.1) |

41.1 (5.1) |

| Record low °F (°C) | −13.9 (−25.5) |

−6.5 (−21.4) |

0.7 (−17.4) |

15.9 (−8.9) |

31.4 (−0.3) |

39.4 (4.1) |

45.4 (7.4) |

40.2 (4.6) |

33.8 (1.0) |

22.7 (−5.2) |

9.8 (−12.3) |

−3.5 (−19.7) |

−13.9 (−25.5) |

| Average precipitation inches (mm) | 3.54 (90) |

2.89 (73) |

3.74 (95) |

4.25 (108) |

4.24 (108) |

4.34 (110) |

5.11 (130) |

4.12 (105) |

4.45 (113) |

4.56 (116) |

3.83 (97) |

4.20 (107) |

49.27 (1,251) |

| Average relative humidity (%) | 68.6 | 64.5 | 60.7 | 58.9 | 64.0 | 70.4 | 69.9 | 72.5 | 73.4 | 71.7 | 69.6 | 70.1 | 67.9 |

| Average dew point °F (°C) | 19.4 (−7.0) |

20.8 (−6.2) |

26.3 (−3.2) |

36.1 (2.3) |

47.5 (8.6) |

58.4 (14.7) |

62.4 (16.9) |

62.1 (16.7) |

55.6 (13.1) |

44.4 (6.9) |

34.4 (1.3) |

24.5 (−4.2) |

41.1 (5.1) |

| Source: PRISM[46] | |||||||||||||

| Climate data for Doylestown, Pennsylvania | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Month | Jan | Feb | Mar | Apr | May | Jun | Jul | Aug | Sep | Oct | Nov | Dec | Year |

| Mean daily maximum °F (°C) | 39 (4) |

43 (6) |

52 (11) |

63 (17) |

74 (23) |

82 (28) |

87 (31) |

85 (29) |

77 (25) |

66 (19) |

55 (13) |

44 (7) |

64 (18) |

| Mean daily minimum °F (°C) | 24 (−4) |

25 (−4) |

33 (1) |

42 (6) |

52 (11) |

61 (16) |

66 (19) |

65 (18) |

57 (14) |

45 (7) |

37 (3) |

29 (−2) |

45 (7) |

| Average precipitation inches (mm) | 3.94 (100) |

2.87 (73) |

4.24 (108) |

3.85 (98) |

4.81 (122) |

3.61 (92) |

4.72 (120) |

4.34 (110) |

4.66 (118) |

3.35 (85) |

3.74 (95) |

3.80 (97) |

47.93 (1,217) |

| Source: Weather Channel[47] | |||||||||||||

Atlantic Coastal Plain Region

[edit]According to the Trewartha climate classification system, the Atlantic coastal plain section of Bucks County, which is located roughly southeast of U.S. Route 1 has a Temperate Oceanic Climate with hot and slightly humid summers, cool winters and year-around precipitation (Doak). Doak climates are characterized by all months having an average mean temperature > 32.0 °F (0 °C), four to seven months with an average mean temperature ≥ 50.0 °F (10 °C), at least one month with an average mean temperature ≥ 72.0 °F (22 °C) and no significant precipitation difference between seasons. According to the Köppen climate classification, this region has a humid subtropical climate (Cfa). During the summer months in the Atlantic Coastal Plain, episodes of extreme heat and humidity can occur with heat index values > 110 °F (43 °C). The average wettest month is July which corresponds with the annual peak in thunderstorm activity. During the winter months, episodes of extreme cold and wind can occur with wind chill values < −7 °F (−22 °C). The plant hardiness zone in Andalusia, Bensalem Twp, elevation 16 ft (4.9 m), is 7a with an average annual extreme minimum air temperature of 3.0 °F (−16 °C).[45] The average seasonal (Nov-Apr) snowfall total is between 24 and 26 inches (61 and 66 centimetres) depending on elevation and distance from the Atlantic Ocean. The average snowiest month is February which correlates with the annual peak in nor'easter activity.

| Climate data for Andalusia, Bensalem Twp. Elevation: 16 ft (4.9 m). 1981-2010 Averages (1981-2018 Records) | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Month | Jan | Feb | Mar | Apr | May | Jun | Jul | Aug | Sep | Oct | Nov | Dec | Year |

| Record high °F (°C) | 72.5 (22.5) |

78.7 (25.9) |

87.7 (30.9) |

94.1 (34.5) |

96.1 (35.6) |

97.5 (36.4) |

103.5 (39.7) |

101.3 (38.5) |

99.1 (37.3) |

89.6 (32.0) |

81.8 (27.7) |

76.6 (24.8) |

103.5 (39.7) |

| Mean daily maximum °F (°C) | 41.0 (5.0) |

44.4 (6.9) |

52.6 (11.4) |

63.9 (17.7) |

73.7 (23.2) |

82.9 (28.3) |

86.9 (30.5) |

85.5 (29.7) |

78.7 (25.9) |

67.3 (19.6) |

56.4 (13.6) |

45.4 (7.4) |

65.0 (18.3) |

| Daily mean °F (°C) | 33.4 (0.8) |

36.0 (2.2) |

43.3 (6.3) |

53.8 (12.1) |

63.3 (17.4) |

72.8 (22.7) |

77.4 (25.2) |

76.0 (24.4) |

68.9 (20.5) |

57.3 (14.1) |

47.6 (8.7) |

37.8 (3.2) |

55.7 (13.2) |

| Mean daily minimum °F (°C) | 25.6 (−3.6) |

27.6 (−2.4) |

34.1 (1.2) |

43.6 (6.4) |

52.9 (11.6) |

62.7 (17.1) |

67.8 (19.9) |

66.4 (19.1) |

59.1 (15.1) |

47.3 (8.5) |

38.9 (3.8) |

30.3 (−0.9) |

46.4 (8.0) |

| Record low °F (°C) | −7.4 (−21.9) |

−0.6 (−18.1) |

5.7 (−14.6) |

19.5 (−6.9) |

35.2 (1.8) |

44.4 (6.9) |

51.0 (10.6) |

45.4 (7.4) |

38.8 (3.8) |

27.6 (−2.4) |

15.0 (−9.4) |

1.6 (−16.9) |

−7.4 (−21.9) |

| Average precipitation inches (mm) | 3.52 (89) |

2.73 (69) |

4.23 (107) |

3.88 (99) |

4.20 (107) |

4.18 (106) |

4.97 (126) |

4.34 (110) |

4.14 (105) |

3.71 (94) |

3.46 (88) |

3.93 (100) |

47.29 (1,201) |

| Average relative humidity (%) | 64.2 | 60.9 | 56.1 | 56.5 | 60.7 | 62.8 | 64.1 | 66.2 | 66.8 | 66.9 | 65.5 | 66.4 | 63.1 |

| Average dew point °F (°C) | 22.6 (−5.2) |

23.8 (−4.6) |

28.7 (−1.8) |

38.7 (3.7) |

49.5 (9.7) |

59.4 (15.2) |

64.3 (17.9) |

63.9 (17.7) |

57.4 (14.1) |

46.4 (8.0) |

36.6 (2.6) |

27.6 (−2.4) |

43.3 (6.3) |

| Source: PRISM[46] | |||||||||||||

| Climate data for Newbold Channel, Falls Twp, Delaware River Water Temperature | |||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Month | Jan | Feb | Mar | Apr | May | Jun | Jul | Aug | Sep | Oct | Nov | Dec | Year |

| Daily mean °F (°C) | 37 (3) |

37 (3) |

44 (7) |

53 (12) |

63 (17) |

74 (23) |

81 (27) |

80 (27) |

73 (23) |

60 (16) |

48 (9) |

40 (4) |

58 (14) |

| Source: NOAA[48] | |||||||||||||

Ecology

[edit]According to the A. W. Kuchler U.S. potential natural vegetation types, Bucks County, Pennsylvania would have a dominant vegetation type of Appalachian Oak (104) with a dominant vegetation form of Eastern Hardwood Forest (25).[49]

Notable people

[edit]- Charles Albright, (1830–1880), United States Congressman; born in Bucks County[50]

- Christy Altomare (1986–), Actress and singer-songwriter, originated the role Anya in the musical Anastasia.[51]

- Jacob Jennings Brown (1775–1828), Commanding General of the United States Army.[52]

- Sabrina Carpenter (1999–), Actress and singer-songwriter

- Ulric Dahlgren (1842–1864), Union Army Colonel, unsuccessful raid on Richmond, Virginia started the Dahlgren Affair.[53]

- Charles Ellet, Jr. (1810–1862), Civil Engineer and Union Army officer.[54]

- Samuel Hartsel (1834–1918), Colorado ranching pioneer.[55]

- Michael Hurley (1941–), singer and guitarist.[56]

- Saige Martin, former member of the Raleigh City Council.[57]

- P!NK (1979–), singer-songwriter.

- Rembrandt Peale (1778–1860), portrait painter and museum keeper.[58]

- Allen Rosenberg (1931–2013), rower and rowing coach[59]

- Andrew Jackson Smith (1815–1897), Union army general

- Arthur Donaldson Smith (1866–1939), explorer of East Africa

- Ezra Stone (1917–1994), actor and director[60]

Official seal

[edit]The traditional seal of Bucks County, Pennsylvania takes its design from the inspiration of the county's founder, William Penn. The center of the seal consists of a shield from the Penn family crest with a tree above and a flowering vine surrounding it in symmetric flanks. The seal has a gold-colored background and a green band denoting Penn as the county's first proprietor and governor.

In 1683, Penn's council decreed that a tree and vine be incorporated into the emblem to signify the county's abundance of woods. The seal was used in its official capacity until the Revolutionary War. The county government has since used the official Pennsylvania state seal for official documents. Today, the Bucks County seal's use is largely ceremonial. It appears on county stationery and vehicles as a symbol of the county's heritage. The gold emblem is also the centerpiece of the official Bucks County flag, which has a blue background and gold trim.

See also

[edit]References

[edit]- ^ Includes Philadelphia, Montgomery, Bucks, Delaware, Chester, Lehigh and Northampton Counties

- ^ "PHMC Historical Markers Search". Pennsylvania Historical and Museum Commission. Commonwealth of Pennsylvania. Archived from the original (Searchable database) on March 21, 2016. Retrieved January 25, 2014.

- ^ "Census - Geography Profile: Bucks County, Pennsylvania". Retrieved April 24, 2022.

- ^ "Find a County". National Association of Counties. Archived from the original on May 31, 2011. Retrieved June 7, 2011.

- ^ "2010 Census Gazetteer Files". United States Census Bureau. August 22, 2012. Retrieved March 5, 2015.

- ^ "U.S. Decennial Census". United States Census Bureau. Retrieved March 5, 2015.

- ^ "Historical Census Browser". University of Virginia Library. Retrieved March 5, 2015.

- ^ Forstall, Richard L., ed. (March 24, 1995). "Population of Counties by Decennial Census: 1900 to 1990". United States Census Bureau. Retrieved March 5, 2015.

- ^ "Census 2000 PHC-T-4. Ranking Tables for Counties: 1990 and 2000" (PDF). United States Census Bureau. April 2, 2001. Archived (PDF) from the original on March 27, 2010. Retrieved March 5, 2015.

- ^ a b "State & County QuickFacts". United States Census Bureau. Archived from the original on August 6, 2011. Retrieved August 30, 2014.

- ^ "U.S. Census website". United States Census Bureau. Retrieved January 31, 2008.

- ^ "P2 HISPANIC OR LATINO, AND NOT HISPANIC OR LATINO BY RACE – 2020: DEC Redistricting Data (PL 94-171) – Bucks County, Pennsylvania".

- ^ "Top 10 U.S. Biopharma Clusters". September 23, 2018.

- ^ Waymarking GPS page about history of Schofield Ford Bridge Retrieved October 13, 2010

- ^ "2020 CENSUS - SCHOOL DISTRICT REFERENCE MAP: Bucks County, PA" (PDF). U.S. Census Bureau. Retrieved July 16, 2024. - Text list

- ^ "Home".

- ^ "About". Bucks County Free Library. Retrieved October 28, 2021.

- ^ Crowther, Prudence. "When the Delay is the Gratification: Allen Saalburg," Art in Print Vol. 7 No. 4 (November–December 2017), 31.

- ^ "The Man Who Was Gene Ween, Back From The Bottom". NPR.org.

- ^ "Archives - Philly.com". The Philadelphia Inquirer. Archived from the original on October 20, 2012.

- ^ a b "The Discoverers Movie". www.discoverersmovie.com.

- ^ "Inqlings: Indie film bringing yuks to Bucks".

- ^ [1] [dead link]

- ^ "Another day on the set for film-industry locals". March 30, 2010.

- ^ Net, Gerard Butler Dot. "Gerard Butler dot Net - Press Room - Latest News". www.gerardbutler.net. Archived from the original on July 23, 2011. Retrieved December 17, 2010.

- ^ "The Happening Movie Blog". thehappeningmovie.blogspot.com.

- ^ "Party, too, was a real happening". September 25, 2007.

- ^ "The Last Game (TV Movie 2002)". IMDb.

- ^ "AmericanRugbyNews.com Pier 40 Action". Archived from the original on July 27, 2010. Retrieved July 31, 2010.

- ^ "USARL | USA Rugby League | American Rugby League « Uncategorized « USA Rugby League Season V announced with 14 teams". Archived from the original on February 2, 2015. Retrieved February 2, 2015.

- ^ [2] Archived October 20, 2011, at the Wayback Machine

- ^ "Bucks County Horse Park".

- ^ "Dark Hollow Park".

- ^ "Pennsbury Manor official website". Retrieved October 8, 2014.

- ^ "Arriving Passengers". Philadelphia International Airport. Retrieved January 8, 2023. - the page lists "Bucks, Chester, Delaware & Montgomery Counties" in its arrival information page

- ^ Leip, David. "Dave Leip's Atlas of U.S. Presidential Elections". uselectionatlas.org.

- ^ "Commissioners | Bucks County, PA". www.buckscounty.gov. Retrieved January 3, 2022.

- ^ Reed, Bill (February 29, 2012). "Fourth Bucks official sentenced in political corruption case". Philadelphia Inquirer. Retrieved October 19, 2023.

- ^ "Bucks Elections". buckscountyvotes.org. Archived from the original on November 25, 2016. Retrieved November 25, 2016.

- ^ "Democrats thumb nose at rule of law in Pennsylvania". The Washington Post. November 15, 2024. Archived from the original on November 16, 2024. Retrieved December 9, 2024.

- ^ Pennsylvania Department of State (July 22, 2024). "Current Voter Registration Statistics by County". dos.pa.gov. Retrieved July 23, 2024.

- ^ "Row Officers | Bucks County, PA". www.buckscounty.gov. Retrieved January 4, 2022.

- ^ "Sheriff | Bucks County, PA". www.buckscounty.gov. Retrieved January 3, 2022.

- ^ "Bucks County Sheriff". Officer Down Memorial Page. Retrieved June 5, 2019.

- ^ "2010 U.S. Census website". United States Census Bureau. Retrieved May 25, 2015.

- ^ a b "USDA Interactive Plant Hardiness Map". United States Department of Agriculture. Archived from the original on June 18, 2021. Retrieved August 8, 2019.

- ^ a b "PRISM Climate Group, Oregon State University". Retrieved August 8, 2019.

- ^ Average weather for Doylestown Weather Channel Retrieved September 2, 2019

- ^ "Water Temperature Table of All Coastal Regions". Archived from the original on September 5, 2017. Retrieved August 9, 2019.

- ^ "U.S. Potential Natural Vegetation, Original Kuchler Types, v2.0 (Spatially Adjusted to Correct Geometric Distortions)". Retrieved August 8, 2019.

- ^ Who Was Who in America, Historical Volume, 1607–1896. Marquis Who's Who. 1967.

- ^ Elkin, Michael (February 16, 2023). "Christy Altomare has a Bucks County love story to tell". Bucks County Herald. Retrieved August 5, 2023.

- ^ "Jacob Jennings Brown". www.britannica.com. Retrieved August 6, 2023.

- ^ Thomas, Ben (December 28, 2021). "'THE MAYOR'S REPORT: Union officer Ulric Dahlgren served and died in the Civil War". echo-pilot.com. Retrieved August 6, 2023.

- ^ The National Cyclopedia of American Biography. Volume 4. New York: James T. White & Company. 1895. p. 360. Retrieved February 16, 2022.

- ^ Laura King Van Dusen, "Samuel Hartsel: 1860s Pioneer Rancher, One of Colorado's First Cattlemen. Founded Town of Hartsel", Historic Tales from Park County: Parked in the Past (Charleston, South Carolina: The History Press, 2013), ISBN 978-1-62619-161-7, pp. 21–27.

- ^ Colin Larkin, ed. (1992). The Guinness Encyclopedia of Popular Music (First ed.). Guinness Publishing. p. 1211. ISBN 0-85112-939-0.

- ^ "Saige Martin". www.hillsboroughstreet.org.

- ^ Miller, Lillian B. Rembrandt Peale: A Life in the Arts: 1778–1860. The Historical Society of Philadelphia, Philadelphia, 1985

- ^ "Inductions | Philadelphia Jewish Sports Hall of Fame". Phillyjewishsports.com. Archived from the original on April 25, 2012. Retrieved November 1, 2011.

- ^ "Estate of Ezra Stone and Sara Seegar goes up for auction, show business couple brought celebrity to Bucks County". Bucks Local News. October 3, 2013. Retrieved July 19, 2019.

External links

[edit]- Bucks County Government official website

- Visit Bucks County (official website of county's tourism promotion agency)